US 20060091793A1

## (19) United States

# Patent Application Publication (10) Pub. No.: US 2006/0091793 A1 Baude et al. (43) Pub. Date: May 4, 2006

(54) METHODS AND DISPLAYS UTILIZING INTEGRATED ZINC OXIDE ROW AND COLUMN DRIVERS IN CONJUNCTION WITH ORGANIC LIGHT EMITTING DIODES

(75) Inventors: Paul F. Baude, Maplewood, MN (US); Steven D. Theiss, Woodbury, MN (US); Michael A. Haase, St. Paul, MN (US); Eric W. Hemmesch, Woodbury, MN (US)

> Correspondence Address: 3M INNOVATIVE PROPERTIES COMPANY PO BOX 33427 ST. PAUL, MN 55133-3427 (US)

(73) Assignee: 3M Innovative Properties Company

(21) Appl. No.: 10/979,067

(22) Filed: Nov. 2, 2004

#### **Publication Classification**

(51) **Int. Cl. H01L** 51/00 (2006.01)

#### (57) ABSTRACT

Methods and displays utilize row and column drivers with ZnO channels that control pixel transistors with ZnO channels, which in turn address OLEDs of an array to produce images of a display screen. A display backplane including the ZnO row and column drivers and the OLEDs may be constructed by utilizing aperture masking or a combination of photolithography and aperture masking. Monolithic integration of the ZnO row and column drivers together with the ZnO pixel transistors is thereby achieved.

Fig. 1

Fig. 5

# METHODS AND DISPLAYS UTILIZING INTEGRATED ZINC OXIDE ROW AND COLUMN DRIVERS IN CONJUNCTION WITH ORGANIC LIGHT EMITTING DIODES

#### TECHNICAL FIELD

[0001] The present invention is related to displays including the circuitry included on display backplanes. More particularly, the present invention is related to backplanes of displays where row and column drivers are included in the circuitry of the backplane to control pixel transistors and where organic light emitting diodes are included in the circuitry as the pixel elements that are activated by the pixel transistors.

#### **BACKGROUND**

[0002] Display backplanes are an important component in a display device, such as a liquid crystal display (LCD), organic light emitting diode (OLED) display, or other display technology. Display backplanes include a substrate providing a platform upon which circuitry is created to cause a display screen to display images. Typically, the backplane includes an array of pixel transistors that provide an electrical signal to an array of pixel elements, such as OLED cells, to cause the picture elements or pixels to produce light that results in the image to be viewed. Additional circuitry includes row and column drivers and is typically located separately from the backplane. The row and column drivers decode the incoming video data to individually activate the pixel transistors and thereby individually control the pixels.

[0003] Because the pixel transistors in the typical case are located on the backplane itself, the pixel transistors are formed as thin film transistors (TFFs) and thereby allow for a very thin display screen such as for thin screen computer and television monitors, telephones, and other compact devices. Because the row and column drivers in the typical case are not located on the backplane, they are not necessarily TF Is. However, the row and column drivers occupy separate space, such as on an integrated circuit chip installed on a display circuit board.

[0004] The interconnections between the row and column drivers and the backplane array can be complex. As the number of rows and columns increase, the interconnect density increases. Even when the row and column drivers are silicon chips bonded to the glass, the level of interconnect complexity can become prohibitive.

[0005] It is desirable in some display screen applications to eliminate or dedicate for other purposes the space required for the row and column driver chip and/or to bring the row and column drivers into closer proximity with the pixel transistors. Therefore, it is desirable to move the row and column drivers directly onto the backplane along with the pixel transistors. However, the row and column drivers must have very fast switching capabilities whereby conventional TFT construction utilizing low mobility semiconductor channels such as amorphous silicon becomes problematic

[0006] It is advantageous, particularly for an OLED based display, to have TFTs including a semiconductor with as large an electron mobility as possible. In general, the electron mobility directly affects transistor speed and/or transis-

tor size. Semiconductors like amorphous silicon have field effect mobilities on the order of 0.5 cm<sup>2</sup>/V-sec. Materials such as polysilicon have higher mobilities (greater than 20 cm<sup>2</sup>/V-sec) but require higher processing temperatures and more complex fabrication procedures.

#### SUMMARY

[0007] Embodiments of the present invention address these issues and others by providing displays and methods that utilize row and column drivers and pixel transistors that are monolithically integrated (i.e., patterned concurrently and by substantially the same process) onto a display substrate while also employing OLEDs as the front-plane elements. The row and column drivers as well as the pixel transistors are constructed as TFTs that have zinc oxide (ZnO) channels, which have a sufficiently high mobility to achieve the switching speeds necessary to properly decode the display signals and activate the OLED pixels. The ZnO row and column drivers address the ZnO pixel transistors that activate the OLEDs of an array to form images on the display screen. The TFTs may be patterned through a process involving aperture masks such as repositionable polymeric aperture masks. Alternatively, the TFFs may be patterned through photolithography.

[0008] One embodiment is a display that includes a backplane substrate. A set of thin film transistor row and column drivers that contains ZnO channels is patterned on the backplane substrate. Additionally, a set of pixel thin film transistors that contain ZnO channels is monolithically integrated with the set of thin film transistor row and column drivers on the backplane substrate. A set of organic lightemitting diodes is patterned on the backplane substrate. Each organic light-emitting diode, which includes a stack of layers, is activated to produce light by a corresponding one or more pixel thin film transistors of the set, and the corresponding one or more pixel thin film transistors are addressed by the set of thin film transistor row and column drivers.

[0009] Another embodiment is a method of creating a display. The method involves patterning a set of ZnO channel thin film transistor row and column drivers on a backplane substrate. The method further involves patterning a set of ZnO channel pixel thin film transistors on the backplane substrate such that the pixel thin film transistors are in electrical connection with the thin film row and column drivers. The method also involves patterning a set of organic light emitting diodes in electrical connection with the pixel thin film transistors. Each organic light emitting diode includes a stack of layers.

[0010] Another embodiment is a method of creating a video display backplane. This method involves utilizing polymeric aperture masking to define ZnO channel row and column drivers and ZnO channel pixel thin film transistors on a backplane substrate. This method further involves utilizing polymeric aperture masking to define organic light-emitting diodes on the backplane substrate.

#### DESCRIPTION OF THE DRAWINGS

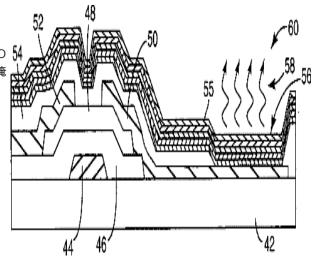

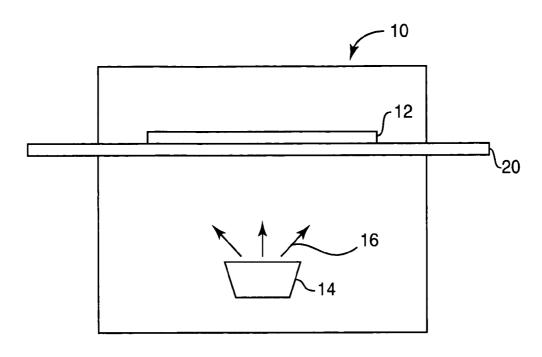

[0011] FIG. 1 illustrates an aperture masking process that may be utilized to construct the ZnO row and column drivers, ZnO pixel transistors, and OLEDs atop a common substrate.

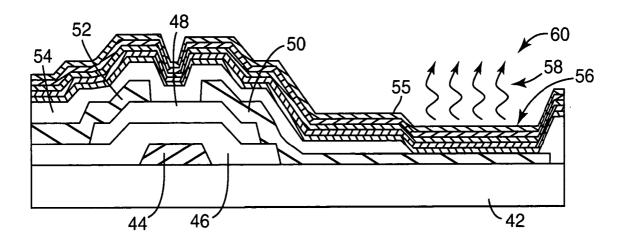

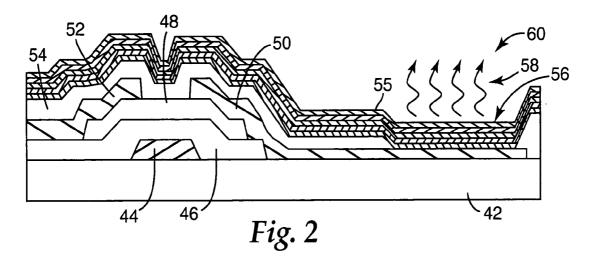

[0012] FIG. 2 illustrates a cross-sectional view of one example of a substrate having a ZnO TFT pixel transistor driving a top emitting OLED stack, which emits light away from the substrate.

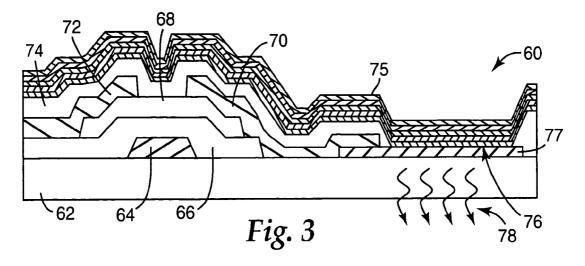

[0013] FIG. 3 illustrates a cross-sectional view of another example of a substrate having a ZnO TFT pixel transistor driving a bottom emitting OLED stack, which emits light through the substrate.

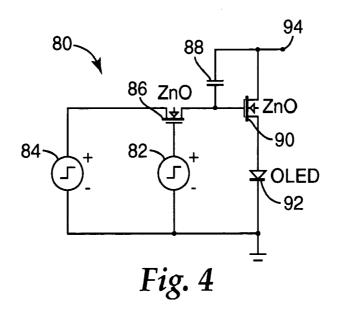

[0014] FIG. 4 is an illustrative example of one cell of ZnO pixel transistors and OLED circuitry forming a single pixel of a display.

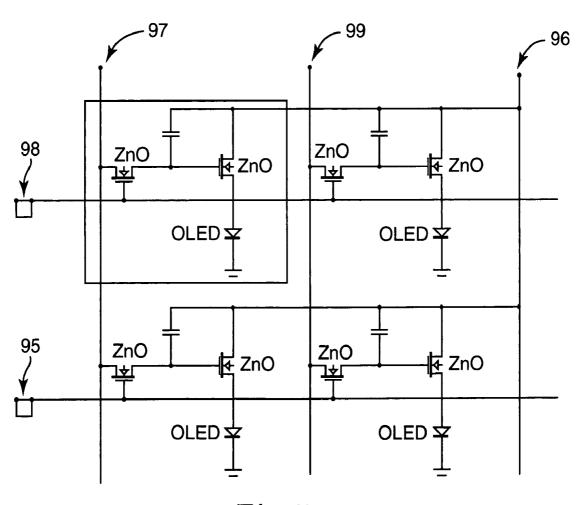

[0015] FIG. 5 is an illustrative example of an array of cells of ZnO pixel transistors and OLED circuitry forming an array of pixels of a display.

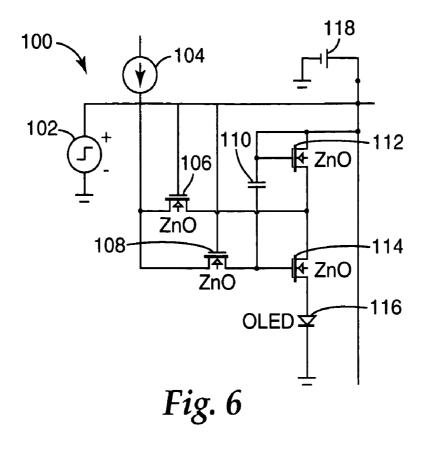

[0016] FIG. 6 is an illustrative example of one cell of ZnO pixel transistors and OLED circuitry forming a single pixel of a display.

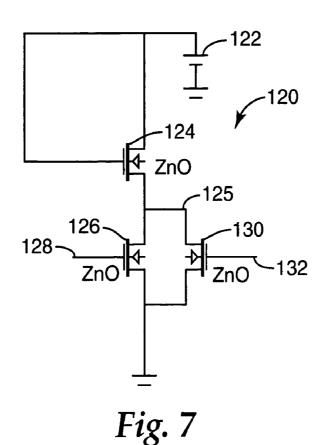

[0017] FIG. 7 is an illustrative example of a ZnO TFT based digital logic gate that is used to create row and column driver circuitry that interfaces with arrays of cells such as shown in FIG. 5 that are based on the circuitry of either FIGS. 4 or 6.

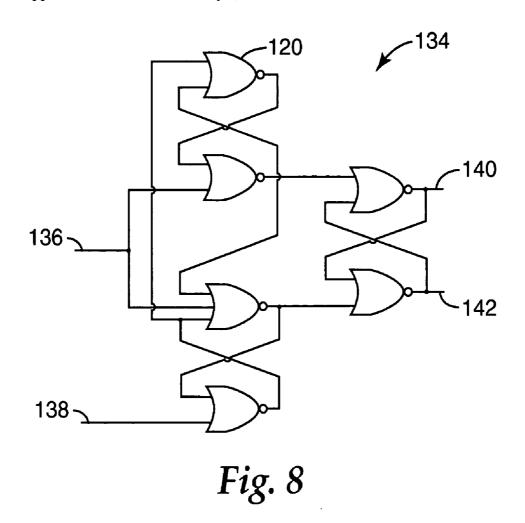

[0018] FIG. 8 is an illustrative example of a digital logic flip-flop that is formed by ZnO TFT based digital logic gates such as those of FIG. 7 to create the row and column driver circuitry.

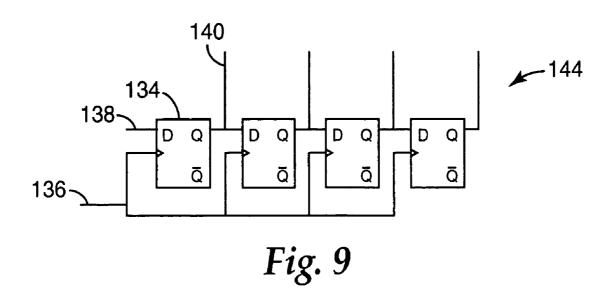

[0019] FIG. 9 is an illustrative example of a digital logic shift register that is formed by ZnO TFT based digital logic flip-flops such as those of FIG. 8 to provide a row or column driver circuit.

#### DETAILED DESCRIPTIONS

[0020] Embodiments of the present invention provide display backplanes having the combination of ZnO row and column drivers integrated onto the same substrate as ZnO pixel transistors and OLEDs. These embodiments provide the superior viewing characteristics of OLEDs with the compactness of integrated row and column drivers. Furthermore, certain embodiments provide for the construction of the backplane utilizing polymeric aperture masking to pattern the ZnO row and column drivers, the ZnO pixel transistors, and the OLEDs. Certain of these embodiments provide for the efficient use of a polymeric aperture masking process resulting in a high yield for the backplane construction while benefiting from the superiority of OLEDs with a reduced likelihood of OLED damage during manufacture.

[0021] Various techniques known in the art may be utilized to pattern the transistors. For example, in some embodiments, photolithography may be utilized to pattern the TFTs followed by utilizing an aperture mask to pattern OLED layers. In other embodiments, wet chemical processing may be avoided altogether as aperture masks may be utilized to pattern the OLED stack as well as the TFTs used as the row and column drivers and the pixel TFTs.

[0022] As noted, in certain embodiments of the present invention, the transistors can be prepared using an aperture mask, such as a shadow mask. Illustrative procedures utilizing aperture masks are set forth in U.S. patent applications Ser. Nos. 2003/0152691 and US2003/0150384, incorporated

herein by reference. To further illustrate the aperture masking process, FIG. 1 is a simplified block diagram of a deposition station that can use an aperture mask for patterning the OLED stack as well as the TFT row and column drivers and pixel TFTs. In particular, deposition station 10 can be constructed to perform a vapor deposition process in which material is vaporized and deposited on a deposition substrate through an aperture mask. The deposited material may be any material necessary for the OLED layers or TFT layers including semiconductor material, dielectric material, or conductive material used to form a variety of elements. For example, organic or inorganic materials may be deposited. In some cases, both organic and inorganic materials can be deposited.

[0023] An aperture mask 20, formed with aperture mask patterns passes through deposition station 10 such that the aperture mask can be placed in proximity with a display backplane substrate 12. Backplane substrate 12 may comprise any of a variety of materials depending on the desired display circuit to be created. For example, backplane substrate 12 may comprise a flexible material or alternatively a rigid material. Any backplane substrates such as glass substrates, silicon substrates, rigid plastic substrates, metal foils coated with an insulating layer, or the like, could also be used. In any case, the backplane substrate 12 may or may not include previously formed features, such as where the TFTs are first patterned onto the backplane substrate 12 using photolithography and at least one layer of the OLEDs are subsequently patterned using the aperture mask. In some examples, all layers of the OLEDs are patterned using the aperture mask.

[0024] Deposition station 10 is typically a vacuum chamber. After a pattern in aperture mask 20 is secured in proximity to backplane substrate 12, material 16 is vaporized by deposition unit 14. For example, deposition unit 14 may include a boat of material that is heated to vaporize the material. The vaporized material 16 deposits on backplane substrate 12 through the deposition apertures of aperture mask 20 to define at least a portion of a circuit layer on backplane substrate 12. Upon deposition, material 16 forms a deposition pattern defined by the pattern in aperture mask 20. Aperture mask 20 may include apertures and gaps that are sufficiently small to facilitate the creation of small circuit elements using the deposition process as described above. Additionally, the pattern of deposition apertures in aperture mask 20 may have a large dimension as mentioned above. Other suitable deposition techniques include e-beam evaporation, various forms of sputtering, and pulsed laser deposition. Example 1, referenced below in relation to FIGS. 2 and 3, includes details for one illustrative method of patterning the TFTs and OLEDs by utilizing aperture masks.

[0025] Thus, utilizing an aperture mask as discussed above is one manner for depositing the TFTs making up the row and column drivers and the pixel TFTs of the display backplane. Furthermore, an aperture mask as discussed above is also one manner for patterning one or more of the layers of the OLEDs that are also present on the substrate adjacent to the pixel TFT. A cross-section of the OLED deposited adjacent the pixel TFT for activating the OLED is shown in the examples of FIGS. 2 and 3. In some devices, all layers of the OLED stack are patterned using an aperture mask.

[0026] It can be beneficial to utilize a polymeric aperture mask, constructed from materials such as polyimide. Advantages of using polymeric aperture masks for patterning the OLED stack include potentially less damage to the OLED material by the aperture mask and the ability to stretch the aperture mask to mitigate dimensional changes in the mask due to various causes such as thermal expansion.

[0027] As an alternative to aperture mask procedures, the ZnO based TFT circuitry may be produced by photolithography while the OLEDs are separately deposited via an aperture mask procedure discussed above. Well-known photolithography techniques may be utilized for defining the ZnO pixel circuitry. Examples of such photolithography techniques are disclosed in Badih El-Kareh, Fundamentals of Semiconductor Processing Technologies, Kluwer Academic Publishers, Chapter 4, pages 590-592, Boston, (1995). Additionally, Example 2, referenced below with respect to FIGS. 2 and 3, includes details for an illustrative process of applying photolithography to first pattern the TFTs followed by application of a shadow mask to pattern the OLED stack. Accordingly, the aperture mask process of FIG. 1 is provided for purposes of illustration and is not intended to be limiting as to the manner for patterning the TFTs of the display.

[0028] The example of FIG. 2 shows the deposition of the pixel TFT and OLED atop a common substrate 42. In this example, the OLED is top emitting (i.e., emits away from rather than through the substrate). As noted above with reference to FIG. 1, the substrate 42 may be constructed of various materials such as glass and other rigid materials or may be made flexible through the use of materials such as metal foil, and plastic (e.g., polyimide, PEN). A gate electrode 44, constructed of materials such as titanium and gold, is directly patterned onto the substrate 42 and then a gate dielectric 46 such as SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> is patterned atop the gate electrode 44 to entirely isolate the gate electrode 44 from the semiconductor channel 48. The semiconductor channel 48 is a layer of ZnO that is patterned atop the gate dielectric 46.

[0029] A drain electrode 52, constructed of materials such as aluminum, is patterned on one side of the channel 48 while a separate source electrode 50 is patterned on the other side of the channel 48 and may be constructed of the same material as the drain electrode 52. The source electrode 50 extends onto the substrate 42 and is positioned between the substrate 42 and the OLED stack 56. An encapsulant layer 54, constructed of materials such as a photoimageable epoxy or other material such as SiO2, is patterned over the layers of the TFT including the source/drain electrodes 50, 52 and the channel 48 while leaving a void above the area of the source electrode 50 where the OLED stack 56 is patterned. It should be noted that the use of the terms source and drain are somewhat arbitrary as it will be appreciated that the electrode contacting the OLED stack 56 may be either the source or the drain, depending upon the circuit design that is chosen.

[0030] Typically, the source electrode and drain electrode features are patterned such that a channel length of about 1 micrometer to about 50 micrometers (preferably about 5 micrometers to about 20 micrometers) separates them. For photolithographically patterned TFTs, the gate length may be as small as 1 micrometer, with 5 micrometers being typical. For aperture mask patterned TFTs, the gate length is

more likely to be 5 to 60 micrometers with a typical gate length of 20 to 30 micrometers.

[0031] The steps of one illustrative process for patterning the layers of the TFTs, including the pixel TFT of FIG. 2, are set forth in detail in Example 1 where the TFTs are patterned by use of an aperture mask. Likewise, the steps of another illustrative process for patterning the layers of the TFTs including the pixel TFT of FIG. 2 are set forth in detail in Example 2 where the TFTs are patterned by photolithography. In either case, the TFTs may be patterned at the substantially same time and through substantially the same process such that the TFT row and column drivers and the pixel TFTs are monolithically integrated onto the display substrate 42.

[0032] The OLED stack 56 is constructed of a stack of organic materials. These materials and their particular order within the stack 56 for one illustrative example are set forth in Examples 1 and 2. To complete a path for current through the OLED stack 56, a top electrode 55 is patterned over the top of the OLED stack 56. This top electrode 55 is constructed of a transparent material such as indium tin oxide (ITO) or a thin metal layer so that the light may be emitted through the electrode 55. Upon receiving electrical current, the materials of the OLED stack 56 begin to emit light.

[0033] In operation of the configuration of FIG. 2, voltage is applied to the drain electrode 52. However, very little current is passed to the source electrode 50 unless voltage is also applied to the gate electrode 44 as the channel 48 remains in a non-conductive state. Upon application of voltage to the gate electrode 44, the channel 48 becomes conductive and current flows through the channel to the source electrode 50 and through the OLED stack 56, thereby causing the OLED to emit light 58 away from the substrate 42. Accordingly, an array of OLEDs addressed in this manner results in an image being displayed.

[0034] The example of FIG. 3 shows the deposition of the pixel TFT and OLED atop a common transparent substrate 62, constructed of materials such as glass or a transparent plastic where the OLED is bottom emitting (i.e., emits light through the substrate). A gate electrode 64 is directly patterned onto the substrate 62 and then a gate dielectric 66 is patterned atop the gate electrode 64 to entirely isolate the gate electrode 64 from the semiconductor channel 68. The semiconductor channel 68 again is a layer of ZnO that is patterned atop the gate dielectric 66. A drain electrode 72 is patterned on one side of the channel 68 while a separate source electrode 70 is patterned on the other side of the channel 68. The source electrode 70 makes contact with a transparent OLED electrode 77, such as an ITO electrode, so that the OLED may emit light through the electrode 77 and substrate 62. An encapsulant layer 74, again constructed of materials such as a photoimageable epoxy or other material such as SiO2, is patterned over the layers of the TFT including the source/drain electrodes 70, 72 and the channel 68 while leaving a void above the area of the transparent electrode 77 where the OLED stack 76 is patterned. A top electrode 75 is deposited atop the OLED stack 76.

[0035] In operation, voltage is applied to drain electrode 72. However, little current is passed to the source electrode 70 unless voltage is also applied to the gate electrode 64 as the channel 68 remains in a non-conductive state. Upon application of voltage to the gate electrode 64, the channel

68 becomes conductive and current flows through the channel to the source electrode 70 and through the OLED stack 76, thereby causing the OLED to emit light 78 through the electrode 77 and substrate 62. A matrix of OLEDs addressed in this manner results in an image being displayed.

[0036] While not specifically discussed above, it will be appreciated that the OLED may be protected from exposure to ambient elements by including an encapsulant that encloses the OLED stack of FIGS. 2 and 3. The encapsulants of FIGS. 2 and 3 then further encapsulate the TFTs and the OLED stack.

[0037] FIG. 4 is an illustrative example of circuitry 80 of a single light-emitting cell where two ZnO pixel TFTs are used. A first voltage source 82 provides enable pulses on a periodic basis to gate a ZnO pixel TFT 86. ZnO pixel TFT 86, once switched on, charges capacitor 88 and the gate of ZnO pixel TFT 90 based on the data pulse from a second voltage source 84. Charging the gate of ZnO pixel TFT 90 switches ZnO pixel TFT 90 to a conductive state, thereby allowing current to flow through the OLED 92 from a supply voltage 94 which produces light for forming an image. The first voltage source 82 that is providing enable pulses represents the output from row driver circuitry discussed below in relation to FIGS. 7-9, while the second voltage source 84 that is providing data pulses represents the output from column driver circuitry also discussed below in relation to FIGS. 7-9.

[0038] FIG. 5 is an exemplary circuit diagram of an array of light-emitting cells based on the configuration shown in FIG. 4. Four cells are shown for purposes of illustration, and there are two ZnO pixel TFTs per cell in this example. One ZnO pixel TFT of each cell is driven by an enable pulse from output 95, 98 of ZnO TFT based row driver circuitry while each OLED of each cell is further driven by a data pulse from output 97, 99 of ZnO TFT based column driver circuitry to provide power to each OLED from the voltage source 96. Accordingly, the arrays of OLEDs produce images as a result of the decoding by the row and column driver outputs activating the individual OLEDs.

[0039] FIG. 6 is an exemplary circuit diagram that illustrates one alternative light-emitting cell design that is based on ZnO pixel TFTs and that mitigates variation in ZnO TFT parameter variation that might otherwise compromise OLED performance. The generalized circuits of FIGS. 4 and 6, excluding the ZnO aspects of the transistors, are known in the art. Specifically, a circuit layout like that of FIG. 6 is shown and described by Yi He et al, EEEE Electron Device Letters, Vol. 21(12), 590-592 (2000).

[0040] In this circuit of FIG. 6, ZnO transistors 106 and 108 are switched on with a signal from voltage source 102. Current source 104 provides the data during this time and forces ZnO transistor 114 to pass the current from current source 104, while charging storage capacitor 110 to the voltage level necessary to drive ZnO transistor 114 at the desired current level. During this time current will not flow through ZnO transistor 112 if power source 118 is at a lower voltage than the drain electrode of ZnO transistor 114. This process accommodates transistor threshold voltage shifts that may occur over time. Current through ZnO pixel transistor 114 then activates OLED 116 to emit light. When the select signal from power source 102 is turned off, ZnO transistors 106 and 108 are turned off, but current now

sourced by voltage source 118 continues to flow though ZnO transistor 114 and OLED 116 as long as storage capacitor 110 remains charged. The cell of FIG. 6 may also be extended to produce an array of cells similar that shown in FIG. 5.

[0041] FIG. 7 is an exemplary circuit diagram that illustrates ZnO TFT based digital logic gates that may be used as the building blocks of row and column driver circuitry which produces the enable and data pulses discussed above in relation to FIGS. 4-6. The particular logic gate of FIG. 7 is an example of a "NOT OR" (NOR) gate 120. However, it will be appreciated that other logic gate designs formed of ZnO TFTs may be utilized as the building blocks of the row and column driver circuitry, such as OR, AND, "EXCLU-SIVE OR" (XOR) logic gates. In this example, a first ZnO TFT 124 receives power from a voltage source 122. TFT 124 remains in a conductive state and an output 125 is taken from the source of the TFT 124. However, the output 125 is also connected to the drain of ZnO TFT 126 and ZnO TFT 130. If a logic high is provided at either gate 128 of TFT 126 or gate 132 of TFT 130, then the output 125 is pulled to a logic low.

[0042] In embodiments of the present invention, these logic gates 120 are formed by the ZnO based TFTs 124, 126, 130 being patterned on the backplane substrate in the electrical configurations shown along with the ZnO based pixel TFTs and OLEDs. The ZnO TFTs of the logic gates may be monolithically integrated with the ZnO based pixel TFTs on the backplane substrate of a display, either by the aforementioned processes of aperture mask based patterning or photolithography based patterning. The patterning of electrical connections of the ZnO based logic gates forming the row and column driver circuitry will become apparent with reference to FIGS. 8 and 9, discussed below.

[0043] FIG. 8 illustrates a standard flip-flop 134, but this flip-flop is formed by a set of interconnected NOR gates 120 that are formed of ZnO based TFTs as shown in FIG. 7 that are monolithically integrated with the ZnO pixel TFTs on the backplane substrate of the display. A clock input 136 is provided as is a data input 138. The flip-flop 134 provides an output 140 and an inverted output 142. It will be appreciated that other logic devices besides flip-flops may be utilized when constructing row and column driver circuits.

[0044] FIG. 9 illustrates a standard shift register 144, but this shift register is formed of cascaded flip-flops 134 as shown in FIG. 8, which are constructed from the logic gates including the ZnO based TFTs patterned on the backplane substrate. The clock 136 and data signals 138 are provided serially from the video data bus of the device producing the display data. In this example, the shift register 144 receives the data bits for the columns of the array of pixels serially but must de-multiplex the serial data by converting the serial data into parallel data. Parallel data allows each pixel to receive its controlling bit or bits simultaneously, as opposed to sequentially. The clock signal 136 propagates the bits down the cascaded flip-flops until the data bit is being provided from the output 140 that corresponds to the proper column of the display. In the simple example shown, the first data bit in is intended for the fourth column so the first data bit has reached its destination column by the fourth clock pulse.

[0045] During the propagation, a row driver circuit, which may also be a logic device such as a set of shift registers,

maintains a logic low output for each row line until the data bits are located at the appropriate column output 140 of the column shift register 144. This timing is based on the number of clock pulses since the last logic high output of the row driver circuit. This prevents the gating transistor, such as transistor 86 of FIG. 4, from passing the incorrect bit to the gate of the pixel transistor directly connected to the OLED. Once the bits are properly aligned with the respective columns, the row driver circuit provides a logic high output to allow the ZnO pixel TFTs gating each output 140 to become conductive. In doing so, the bit for each column is passed to the gate of the ZnO pixel TFT directly connected to the OLED thereby causing the OLED to either emit light or not, depending upon the value of the bit.

[0046] While FIGS. 7-9 provide one example of row and column circuitry, it will be appreciated that there may be many variations of row and column circuitry that are constructed of ZnO based TFTs patterned on the display substrate. Accordingly, FIGS. 7-9 are provided only to illustrate one example of such row and column circuitry.

[0047] Examples 1 and 2 immediately follow and set forth details of patterning the ZnO TFTs and OLEDs on the display substrate. The details of Examples 1 and 2 are each provided only to illustrate separate examples of patterning the ZnO TFTs and OLEDs. It will be appreciated that there may be many variations in both the aperture mask fabrication process and the alternative mixed photolithography-aperture mask fabrication process.

#### **EXAMPLES**

#### Example 1

#### ZnO TFT and OLED Shadow Mask Fabrication Description for a Display

[0048] Integrated circuits are comprised of circuit elements, such as thin film transistors (TFTs) and capacitors, which are formed by vacuum depositing thin films through flexible masks which act to pattern the films. Typical thin film materials are metals for conductors or electrodes, dielectrics for capacitors or to prevent electrical conduction between intersecting metal lines, and semiconductors for the active layer of transistors. Examples of thin film materials are gold, titanium, and aluminum for conductors or electrodes;  $\mathrm{Al_2O_3}$  or  $\mathrm{SiO_2}$  for dielectrics; and sputtered ZnO or thermally evaporated pentacene as semiconductors.

[0049] A 2"×2" glass slide was cleaned by rinsing with alcohol. Polymeric shadow masks were formed as previously described in applicant's publications, U.S. patent applications Ser. No. 2003/0152691 and 2003/0150384, incorporated herein by reference. Apertures were formed in the shadow masks using laser ablation.

[0050] A gate level shadow mask pattern was centered on the glass substrate. 100 Å of e-beamed titanium was deposited in a vacuum chamber on the glass substrate through the shadow mask followed by 750 Å of evaporated gold from a resistive-heater source. The substrate and the shadow mask were removed from the vacuum system. The substrate was cleaned by blowing nitrogen over its surface.

[0051] The gate dielectric was deposited as follows. A shadow mask with apertures for the gate dielectric pattern

was aligned and registered with the gate level deposition patterns on the substrate.  $1600 \text{ Å} \text{ SiO}_2$  was deposited through the shadow mask in a vacuum chamber (450 W). The substrate and the shadow mask were removed from the vacuum system and the substrate was cleaned with a nitrogen blow.

[0052] The ZnO semiconductor was deposited as follows. A shadow mask with apertures for the semiconductor pattern was aligned and registered with the gate dielectric and gate level deposition patterns on the substrate. 500 Å ZnO was deposited in a vacuum chamber (100 W from a 6 inch diameter ZnO target, 10% O<sub>2</sub> in Ar flow at 0.4 sccm.). The substrate and the shadow mask were removed from the vacuum system and the substrate was cleaned with a nitrogen blow.

[0053] The source and drain electrodes (Al) were similarly deposited through appropriate shadow masksby vacuum evaporation from a resistive-heater source. At this point the integrated TFT circuitry was complete.

[0054] An encapsulant was deposited on top of the integrated TFT in order to separate the OLED layers from layers of the TFT and integrated circuit. The encapsulant was deposited by aligning an encapsulant shadow mask with the previously patterned layers. Electron beam evaporated  $Al_2O_3$  was used as the encapsulant. It was deposited by vacuum deposition to a thickness of 3000 Å.

[0055] The OLED stack may then be deposited on top of the encapsulating layer by vacuum evaporating 3000 Å 4,4',4"-tris(N-(3-methylphenyl)-N-phenylamine)triphenylamine (MTDATA) doped with 3% fluorinated tetracyano-quinodimethane (TCNQ), followed by 400 Å N,N'-Bis-(naphthalen-1-yl)-N,N'-bis(phenyl)benzidine (NPB), 300 Å tris-(8-hydroxyquinoline) aluminum (Alq<sub>3</sub>) doped with 10-(2-benzothiazolyl)-1,1,7,7- tetramethyl-2,3,6,7-tetrahydro-1H,5H,11H benzopyrano (6,7,8-ij) quinolizin-11-one (C545T), 200 | Alq<sub>3</sub>, 7 Å LiF (deposited at a rate of 0.5 Å/sec), 50 Å Al, and finally 150 Å Ag.

#### Example 2

#### ZnO TFT Photolithography/OLED Shadow Mask Fabrication Description for a Display

[0056] A 2"×2" glass slide was cleaned using an alcohol rinse. The slide was prebaked at 120° C. for 60 sec. to improve photoresist (PR) adhesion. A negative photoresist (FUTURREX NR7-1000PY, available from Futurrex, Inc, Franklin, N.J.) was applied to the slide by spin coating (5000 RPM spin for 60 seconds, followed by a soft back at 150° C. for 60 seconds). The photoresist was exposed to a gate level mask with 180 mJ/cm<sup>2</sup> and then post exposure baked at 100° C. for 60 seconds. The slide with exposed photoresist was developed using FUTURREX RD6 developer for about 10 seconds. The developed slide was inspected and then rinsed in water followed by drying in nitrogen. Subsequently, 50 Å of electron beamed titanium and 600 Å of gold were vacuum evaporated from an electron-beam and resistive-heater source respectively. The patterning of the gate metal layer was completed by lift-off of the metal in acetone followed by a methanol and water rinse.

[0057] The gate dielectric,  $1600 \text{ Å SiO}_2$ , was sputtered (450 W on an 8 inch diameter  $SiO_2$  target). Next, 500 Å of ZnO (100 W on a 6 inch ZnO target, 10%  $O_2$  in Ar flow at 0.4 sccm) was sputtered

[0058] The ZnO was etched photolithographically as follows. Positive photoresist (FUTURREX PR1-1000A) was applied to the substrate by spin coating at 5000 RPM for 60 seconds followed by a soft bake at 120° C. for 120 seconds. The resist was exposed at 120 mJ/cm² through a photolithography mask The resist was developed by exposure to FUTURREX RD6 developer for 40 seconds. The sample was then inspected, rinsed with water and dried with nitrogen. The substrate was then etched in 0.5% HCl for 6 seconds and the photoresist was then removed.

[0059] The  $\mathrm{SiO}_2$  was etched as follows. The ZnO-etched substrate was prebaked at  $120^{\circ}$  C. for 60 seconds. Positive photoresist was applied to the prebaked substrate (FUTUR-REX PR1-1000A spin coated at 5000 RPM for 60 seconds followed by a soft bake at  $120^{\circ}$  C. for 120 seconds. The resist was exposed through a photolithography mask with  $120~\mathrm{mJ/cm^2}$ , developed using FUTURREX RD6 developer, inspected, rinsed in water and then dried with nitrogen. The substrate was then hard baked at  $120^{\circ}$  C. for 60 seconds. The sample was etched with PAD ETCH 4 (available from Ashland Specialty Chemicals, Dublin, Ohio) for 90 seconds followed by removal of the photoresist.

[0060] The source and drain electrodes were patterned by photolithography as follows. The etched oxide substrate was prebaked at 120° C. for 60 seconds. A layer of negative photoresist (FUTURREX NR7-1000PY) was applied by spin-coating at 5000 RPM for 60 seconds followed by a soft bake at 150° C. for 60 seconds. The photoresist was exposed through a source/drain aperture mask at 180 mJ/cm², post baked at 100° C. for 60 seconds, developed using FUTUR-REX RD6 for 10seconds, inspected, water rinsed and dried in nitrogen. Finally Ti/Au/Ag was sequentially deposited on top of the substrate. The patterning of the source/drain metal layer was completed by lift-off of the deposited metals in acetone followed by a rinse in methanol and water, and nitrogen blow-dry.

[0061] The encapsulant was applied as follows. A negative, epoxy-type photoresist (SU-8-2000.5, available from MicroChem, Newton, Mass.) was filtered through a 0.45 µm filter and then applied to the integrated TFT substrate by spincoating at 5000 RPM for 60 seconds followed by a soft bake at 100° C. for 2 minutes. The sample was exposed through a photomask with an illumination of 54 mJ/cm² followed by a post exposure bake at 100° C. for 2 minutes. The sample was developed in SU-8 DEVELOPER (MicroChem) for 10 seconds followed by rinsing with isopropanol. The sample was hard baked at 150° C. for 2 minutes. The integrated TFT circuitry was complete at this point and ready for the OLED components.

[0062] The OLED stack was deposited on top of the encapsulating layer by vacuum evaporating 3000 Å 4,4',4"-tris(N-(3-methylphenyl)-N-phenylamine)triphenylamine (MTDATA) doped with 3% fluorinated tetracyanoquinodimethane (TCNQ), followed by 400 Å N,N'-Bis(naphthalen-1-yl)-N,N'-bis(phenyl)benzidine (NPB), 300 Å tris-(8-hydroxyquinoline) aluminum (Alq<sub>3</sub>) doped with 10-(2-benzothiazolyl)-1,1,7,7-tetramethyl-2,3,6,7-tetrahydro-1H, 5H,11H benzopyrano (6,7,8-ij) quinolizin-11-one (C545T), 200 Å Alq<sub>3</sub>, 7 Å LiF (deposited at a rate of 0.5 Å/sec), 50 Å Al, and finally 150 Å of Ag.

[0063] While the invention has been particularly shown and described with reference to various embodiments

thereof, it will be understood by those skilled in the art that various other changes in the form and details may be made therein without departing from the spirit and scope of the invention.

What is claimed is:

- 1. A display, comprising:

- a backplane substrate;

- a set of thin film transistor row and column drivers that is patterned on the backplane substrate and that contains ZnO channels;

- a set of pixel thin film transistors that is monolithically integrated with the set of thin film transistor row and column drivers on the backplane substrate and that contain ZnO channels; and

- a set of organic light-emitting diodes comprising a stack of layers patterned on the backplane substrate, wherein each organic light-emitting diode is activated to produce light by a corresponding one or more pixel thin film transistors of the set, and wherein the corresponding one or more pixel thin film transistors are addressed by the set of thin film transistor row and column drivers.

- 2. The display of claim 1, wherein the backplane substrate is flexible.

- 3. The display of claim 2, wherein the backplane substrate is plastic.

- 4. The display of claim 1, wherein the backplane substrate is rigid.

- 5. The display of claim 4, wherein the backplane substrate is glass.

- **6**. The display of claim 1, wherein the set of thin film transistor row and column drivers and the set of pixel thin film transistors are patterned by photolithography and at least one layer of the stack of layers in the the set of organic light-emitting diodes is patterned by polymeric aperture masking.

- 7. The display of claim 1, wherein the set of thin film transistor row and column drivers, the set of pixel thin film transistors, and at least one layer of the stack of layers in the set of organic light-emitting diodes are patterned by polymeric aperture masking.

- **8**. The display of claim 1, wherein the organic light emitting diodes emit away from the backplane substrate.

- **9**. The display of claim 1, wherein the organic light emitting diodes emit through the backplane substrate.

- 10. The display of claim 1, wherein the set of pixel thin film transistors form individual cells that contain four thin film transistors and one organic light-emitting diode per cell.

- 11. The display of claim 1, wherein the thin film transistor row and column drivers have an electron mobility in excess of 4  $\rm cm^2/V$ -sec.

- 12. A method of creating a display, comprising:

patterning a set of ZnO channel thin film transistor row and column drivers on a backplane substrate;

patterning a set of ZnO channel pixel thin film transistors on the backplane substrate, the pixel thin film transistors being in electrical connection with the thin film transistor row and column drivers; and

patterning a set of organic-light emitting diodes on the backplane substrate in electrical connection with the pixel thin film transistors, wherein each organic lightemitting diode comprises a stack of layers.

- 13. The method of claim 12, wherein patterning the set of ZnO channel thin film transistor row and column drivers and patterning the set of ZnO channel pixel thin film transistors on the backplane substrate comprises forming by photolithography.

- 14. The method of claim 12, wherein patterning the set of ZnO channel thin film transistor row and column drivers and patterning the set of ZnO channel pixel thin film transistors on the backplane substrate comprises utilizing polymeric aperture masking.

- 15. The method of claim 12, wherein patterning the set of organic light-emitting diodes on the backplane substrate comprises forming at least one layer of the stack of layers in the organic light-emitting diodes utilizing polymeric aperture masking.

- **16**. A method of creating a video display backplane, comprising:

- utilizing polymeric aperture masking to define ZnO channel row and column drivers and ZnO channel pixel thin film transistors on a backplane substrate; and

- utilizing polymeric aperture masking to define organic light-emitting diodes on the backplane substrate.

- 17. The method of claim 16, wherein utilizing polymeric aperture masking to define ZnO channel row and column drivers and ZnO channel pixel thin film transistors comprises patterning electrical connections between the row and column drivers and the pixel thin film transistors.

- 18. The method of claim 16, wherein utilizing polymeric aperture masking to pattern organic-light emitting diodes on the backplane substrate comprises patterning electrical connections between the pixel thin film transistors and the organic light-emitting diodes.

- 19. The method of claim 16, wherein utilizing polymeric aperture masking to define organic-light emitting diodes on the backplane substrate comprises patterning layers forming the organic light-emitting diodes atop an electrode layer of the pixel thin film transistors.

- **20**. The method of claim 16, further comprising patterning an encapsulant layer over the row and column drivers and the pixel thin film transistors.

\* \* \* \* \*

| 专利名称(译)        | 利用集成氧化锌行和列驱动器以及有机发光二极管的方法和显示器                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | <u>US20060091793A1</u>                                                                                          | 公开(公告)日 | 2006-05-04 |

| 申请号            | US10/979067                                                                                                     | 申请日     | 2004-11-02 |

| [标]申请(专利权)人(译) | 明尼苏达州采矿制造公司                                                                                                     |         |            |

| 申请(专利权)人(译)    | 3M创新有限公司                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 3M创新有限公司                                                                                                        |         |            |

| [标]发明人         | BAUDE PAUL F THEISS STEVEN D HAASE MICHAEL A HEMMESCH ERIC W                                                    |         |            |

| 发明人            | BAUDE, PAUL F. THEISS, STEVEN D. HAASE, MICHAEL A. HEMMESCH, ERIC W.                                            |         |            |

| IPC分类号         | H01L51/00                                                                                                       |         |            |

| CPC分类号         | H01L27/1214 H01L27/3244 H01L27/3248 H01L27/3262 H01L29/7869 H01L2251/5315 H01L2251/5338 H01L27/1225 H01L27/1218 |         |            |

| 其他公开文献         | US7298084                                                                                                       |         |            |

| 外部链接           | Espacenet USPTO                                                                                                 |         |            |

### 摘要(译)

方法和显示利用具有ZnO通道的行和列驱动器,其控制具有ZnO通道的像素晶体管,其反过来解决阵列的OLED以产生显示屏的图像。包括ZnO 54行和列驱动器以及OLED的显示器底板可以通过利用孔掩模或光刻和孔掩模的组合来构造。由此实现ZnO行和列驱动器与ZnO像素晶体管的单片集成。